### Harsh environment interconnection technology for three-dimensional packaging

J. Bickel<sup>1,3</sup>, Joachim Scherer<sup>4</sup>, M. Schneider Ramelow<sup>2,3</sup>, K.-D. Lang<sup>2,3</sup>, H.-D. Ngo<sup>1,2</sup>

<sup>1</sup>University of Applied Sciences, Berlin, Germany | <sup>2</sup>Fraunhofer IZM, Berlin, Germany

<sup>3</sup>Technische Universität Berlin, Berlin, Germany | <sup>4</sup>Aurion Anlagentechnik GmbH, Seligenstadt, Germany

# 1. Motivation

In the field of SiC electronics, more and more improvements have been made in the area of harsh environment in recent years. Especially in terms of high temperature resistance. While initially only simple transistors were used [1], the first more complex circuits in 6H-SiC are now possible [2]. Also in the sector of micromechanical sensors, solutions for temperatures of 500 °C have existed for several years [3] [4]. However, the limiting factor today is often the circumstance of reliable and inexpensive interconnection technology (ICT) and packaging technology. Due to the high temperatures and the different CTEs of different materials that are used, only a few raw materials can be considered for high temperature ITC. Obvious materials are ceramics and for low cost systems especially Al<sub>2</sub>O<sub>3</sub>. Platinum and gold thin wire bonding is suitable for the interconnect level between chip and substrate [5].

#### 2. State of the Art

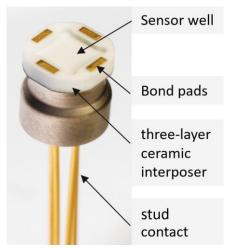

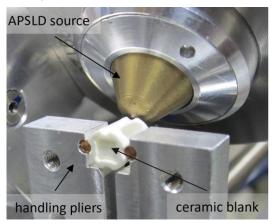

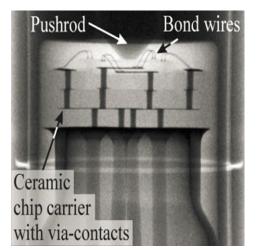

Since Al<sub>2</sub>O<sub>3</sub>, like other ceramics, is difficult to pattern by micro technological methods, the capabilities for ICT are very limited. Thick film pastes of gold and platinum are generally used on planar substrates. [6]. The disadvantages are the increased consumption of resources due to the technological and not the physical limits as well as the fact that no through-hole vias or 3D structures can be realized. Today, a punching through hole stud bonding process is often used to establish electrical connections in three dimensions from the chip level to the environment. With such a system, a very large number of steps are required to place the solid metal stud through the hole in the ceramic. Then, layer by layer, the materials have to be stacked on top of each other. Such a stacked system is shown in Fig. 1 and Fig. 2 and has been used since several years for the application in pressure sensor measuring systems [7].

#### 3. Technical Approach

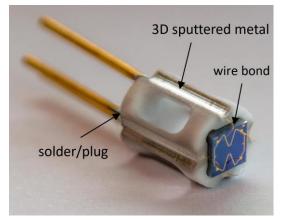

To overcome the drawbacks of existing technologies, we have developed a solution that uses the atmospheric pressure sputtering layer deposition technology (APSLD) [8] to enable signal routing on special 3D printed ceramic substrates using platinum and gold metallization. The APSLD technology is used to additively deposit the metal directly and in a structured process in notches that are located along the side of a cylinder. The metal covers only the surface in the notch, as can be seen in Fig. 3 and Fig. 4. In addition, the metallization coating is applied over the end faces of the cylinder. This allows the ceramic to be subsequently framed and welded as required, including by conductive materials such as Invar or Kovar, and to be contacted from the top and bottom surfaces. Thin-wire wire bonding is very well suited as a contacting solution to the chip level. In this system, SMD solder contacts can be used on the underside, or an FR4 interposer can be attached, as the thermal stress on the underside is no longer in the critical range and since high temperatures no longer exist here.

#### 4. Discussion

Due to the high flexibility of the process, the ceramic geometry can be adapted as required to the environmental conditions and the system used. When applying pure platinum as conductive material, platinum layer thicknesses of 200 - 300 nm can be used for 10 mm long conductors with 10 Ohm resistance and thus technology consumption costs and material costs for the metallisation of only a few cents per conductor can be realized. These are significant cost reductions compared to the solid metal connections in today's standard systems. The conductor can be applied fully automatically to any solid material, eliminating the need for further assembly and handling steps for the manufacture of the package itself.

## **Pictures**

Fig. 1: Real picture of a common high temperature package. Ceramic carrier from Kyocera

Fig. 2: X-ray imaging with sensor and bond wires. Three stacked planes are visible

Fig. 3: Fully automatic production system for 3D APSLD coatings of ceramic blanks

Fig. 4: Prototype of high temperature pressure sensor packaging produced by using APSLD

#### References

1. P. G. Neudeck, et al. 6H-SiC Transistor Integrated Circuits Demonstrating Prolonged Operation at 500 °C. *IMAPS HiTEC.* 2008.

2. M. Shakir, S. Hou, A. Metreveli, A. U. Rashid, H. A. Mantooth, C. M. Zetterling. Shakir, Muhammad, et al. "555-Timer and Comparators Operational at 500° C. *IEEE Transactions on Electron Devices.* 2019.

3. L. Y. Chen, G. W. Hunter, P. G. Neudeck, G. M. Beheim. Packaging technologies for high temperature electronics and sensors. *Joint Conference on 67th Machinery Failure Prevention Technology*. 2013.

4. A. A. Ned, R. S. Okojie and A. D. Kurtz. 6H-SiC pressure sensor operation at 600°C. Fourth International High Temperature Electronics Conference. HITEC. 1998.

5. L. Coppola, D. Huff, F. Wang, R. Burgos and D. Boroyevich. Survey on High-Temperature Packaging Materials for SiC-Based Power Electronics Modules. *IEEE Power Electronics Specialists Conference*. 2007.

6. R. Zeiser, P. Wagner, S. Ayub, J. Wilde, S. Henneck. Flip-chip package for pressure sensors with operationtemperatures up to 500 °C. *AMA Conferences.* 2015.

7. **H. D. Ngo.** Liquid-free SOI-based piezoresistive pressure sensor for measurement up to 400°C. *IEEE Sensors*. Taiwan : s.n., 2012. Vols. S. 100-114.

8. J. Bickel, H.-D. Ngo, M. Schneider Ramelow, K.-D. Lang. Increasing the productivity of the novel atmospheric pressure sputtering technology for 3D chip interconnection. Pisa : IEEE, 2019. ISBN 978-1-7281-6291-1.