# THT-Problemstellen frühzeitig erkennen – Modellbasiertes Design for Manufacturing beim Selektivwellenlöten

Reinhardt Seidel<sup>1)</sup>, und Jörg Franke<sup>1)</sup>

<sup>1)</sup>Lehrstuhl für Fertigungsautomatisierung und Produktionssystematik (FAPS),

Friedrich-Alexander-Universität Erlangen-Nürnberg, 90429 Nürnberg

reinhardt.seidel@faps.fau.de

### Zusammenfassung

THT-Lötstellen führen immer wieder zu Fertigungsproblemen, weil der erforderliche Lotdurchstieg nicht erreicht werden kann. Um derartige Probleme in den Griff zu bekommen sind aussagekräftige Modelle notwendig, die den Lotdurchstieg schon im Designstadium quantifizieren können. Im folgenden Beitrag werden die im AIF IGF Projekt Siwolak [1] erarbeiteten Ansätze zur Berechnung des Lotdurchstiegs dargelegt.

### **Einleitung und Motivation**

Wellen- und Selektivwellenlöten, sind zuverlässige, günstige und weit verbreitete Lötprozesse für das automatisierte Weichlöten von THT-Bauteilen. Die bisher nicht quantitativ bewertbare Weichlötbarkeit im Sinne der thermischen Machbarkeit einer Lötstelle führt regelmäßig zu problematischen Lötstellen in der Fertigung. Dicke Kupferlagen und thermisch massive Bauteile werden insbesondere in Anwendungen der Elektromobilität und der erneuerbaren Energien gefordert. Bei ungeeignetem Kupferlagendesign steigt dadurch jedoch der Lötwärmebedarf über die Lötwärmezufuhr durch die Selektivwelle. Daraus entstehen den Schäden Unternehmen längere Designphasen, durch Fehlerkosten, Fertigungskosten, reduzierte Qualität und somit als Folge verringerte Wettbewerbsfähigkeit. Die Einhaltung etwa firmeninterner, auf Empirie basierender Design-Richtlinien ist dabei nur eingeschränkt zur Linderung des Problems geeignet, da der Wärmebedarf dadurch nicht quantifizierbar ist.

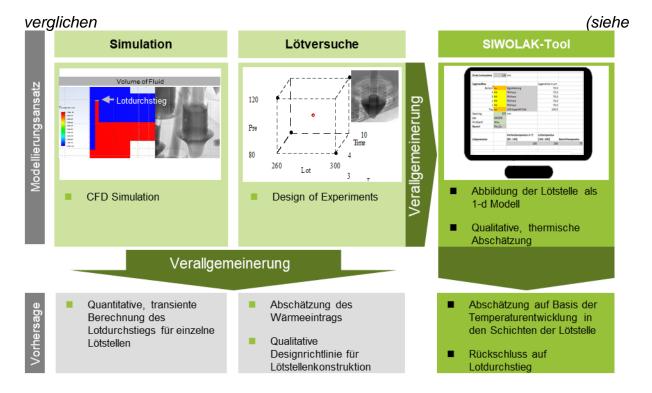

Um dieser Problemstellung zu begegnen, wurde der Selektivlötprozess mittels statistischer Versuchspläne und Simulationsmodellen untersucht und iterativ

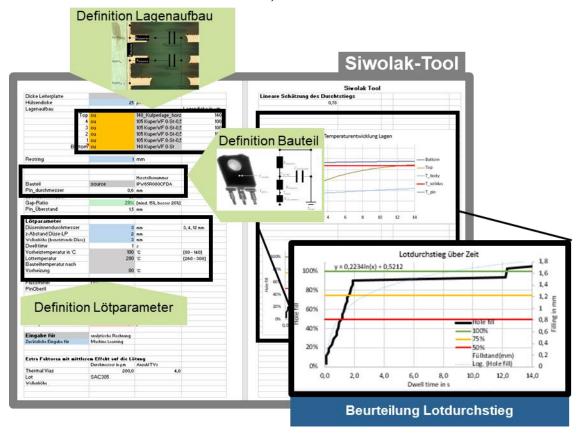

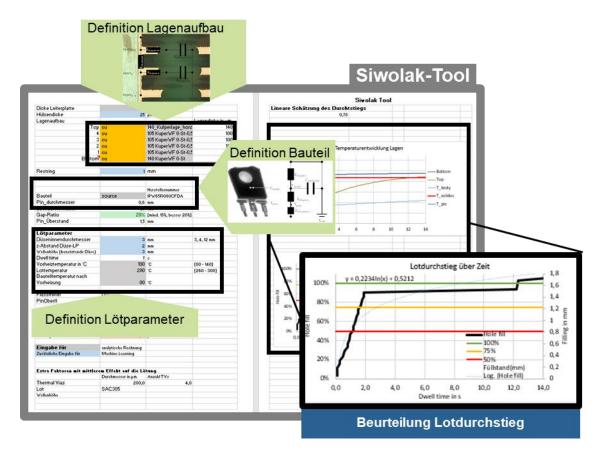

Bild 1). Mit dem Ziel, thermisch kritische Lötstellen früh im Designprozess zu identifizieren sowie computergestützt Lötparameter zu bestimmen, wurde mit den Erkenntnissen ein Excel-Tool entwickelt. Dieses Modell berücksichtigt die wesentlichen Prozesseinflussfaktoren, die thermischen Eigenschaften des Bauteils sowie den Kupferlagenaufbau an jeder Lötstelle. So kann es im Entwicklungsprozess zur Unterstützung eingesetzt werden.

Bild 1: Vorgehen zur Entwicklung eines Modells zur Vorhersage des Lotdurchstiegs

# Ableitung von Designempfehlungen aus experimentellen und numerischen Studien

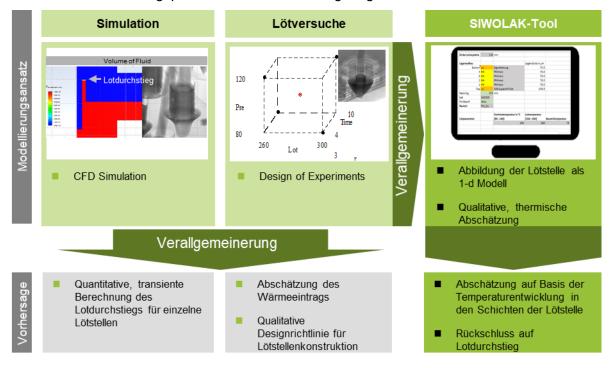

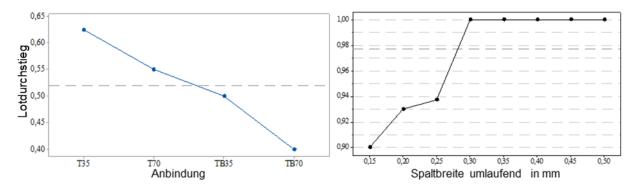

Die Umsetzung eines Multiphysics CFD Modells mittels ANSYS-Fluent erlaubt die Berücksichtigung des Lotspaltstroms als Kapillarstrom mit Hilfe der Volume of Fluid (VOF) Methode in einer parametrisiert konfigurierbaren Lötstelle. Dadurch sind auch quantitativ gute Vorhersagen möglich. Verfahrensbedingt kostet die Vorhersage jedoch sehr viel Rechenzeit. Für das 2D- Modell müssen ca. 1h/Lötsekunde, für das 3D-Modell ca. 24h/Lötsekunde angesetzt werden.

Bild 2: Validierung der Simulationsergebnisse an Hand von Lötversuchen

Zur experimentellen und simulativen Untersuchung des Selektivwellenlötprozesses und der Designvarianten wurden jeweils statistische Versuchspläne durchgeführt. Versuchsvorgehen wird jede Lötstelle einzeln gelötet. So werden reproduzierbare Randbedingungen für die Lötung sichergestellt und Einflüsse des Lötstellendesigns werden nicht von der Lötreihenfolge überlagert. Die untersuchten Einflüsse umfassten typische in der Durchstecktechnologie eingesetzte Bauteiltypen wie Steckerpin, Folienkondensator (Foko), Elektrolytkondensator (Elko) und Metall-Oxid-Halbleiter-Feldeffekttransistor (Mosfet). Das Ankontaktierungsdesign wurde diskret durch Lagenzahl, -dicke und -anbindung sowie Lochspalt und Wärmefallen unterschieden, um detaillierte Aussagen zu den jeweiligen Designsituationen machen zu können. Das untersuchte Prozessfenster erstreckt sich von 260°C bis 300°C Lottemperatur.

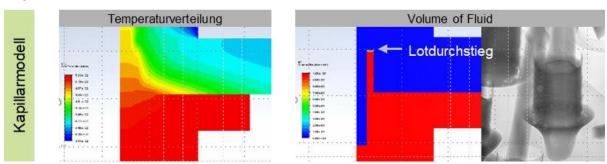

In den Studien wurde besonders der Einfluss des Lagenaufbaus untersucht. Insbesondere die Lagendicke und der Ort der Ankontaktierung spielen hier eine wichtige Rolle, wie oben bereits eingeführt. Im Zusammenhang zeigt Bild 3 den Einfluss einer Anbindung auf Top (T) und Top und Bottom (TB) für 35 und 70 µm. Zudem zeigt sich hier, dass zwei dünnere Lagen (TB35) einen etwas geringeren Durchstieg aufweisen als eine dicke (T70). Der Einfluss der umlaufenden Spaltbreite zwischen Loch und Pin zeigt über verschiedene Ankontaktierungsdesigns gemittelt ebenfalls einen wichtigen Einfluss auf den Lotdurchstieg. Im Hinblick auf den Lochdurchmesser gilt, je größer, desto besser für den Lotdurchstieg.

Normiert auf die Leiterplattendicke ergibt sich ein Gap-Ratio Verhältnis (Gleichung 1) von ca. 35-40% ab dem der Designeinfluss beim Selektivwellenlöten abnimmt. Grund dafür ist, dass bei steigendem Aspektverhältnis von Lochdurchmesser zu Leiterplattendicke die Flussmitteldurchdringung und die durch den größeren Lotmassenstrom eingebrachte Energie verbessert wird. Insbesondere die Flussmitteldurchdringung spielt für dickere Leiterplatten eine wichtige Rolle, da sich das Aspektverhältnis bei gleichbleibenden Spaltbreiten schnell verschlechtert.

$$Gap - Ratio \ [\%] = \frac{d_{loch} - d_{pin}}{Leiterplattendicke}$$

(1)

Bild 3: Experimentelle Ergebnisse des Einflusses der Lagenaufbauten (links) und umlaufender Spaltbreite auf den Lotdurchstieg (rechts)

Aus den Umfangreichen statistischen Versuchsplänen und CFD Simulationsstudien können einige grundlegende Empfehlungen gegeben werden. Bis zu ihrem quasithermischen Gleichgewicht verhält sich die Temperatur der Lötstelle exponentiell wachsend mit Sättigung. Der Einfluss der Lotkontaktzeit ist ab dem quasithermischen Gleichgewicht einer Lötstelle statistisch nicht signifikant. Der Einfluss des Düsendurchmessers ist mitunter erheblich. Durch größere Düsendurchmesser wird über die größere Fläche mehr Wärme eingetragen, was zu deutlich verbessertem Lotdurchstieg führt. Die Lötversuche zeigen, dass die gleichzeitige Lötung aller Bauteilpins zu einer signifikanten Verbesserung des Lotdurchstiegs führen. Das liegt an der simultanen Erwärmung mehrerer vertikaler Durchmetallisierungen in der Leiterplatte, was die Anisotropie der Wärmeleitung des Kupfer-FR4 Schichtaufbaus verringert und das Bauteil an allen Pins erwärmt. Dadurch sinkt auch der Einfluss der thermischen Kapazität des Bauteils.

Hinsichtlich des Lötstellendesigns ist besonders bei thermisch anspruchsvollen Lötstellen mit massiven Kupferanbindungen, Bauteilpins großer thermische Kapazität und/oder großer Kupferquerschnitte auf der Lotzielseite, auf der Lotquellseite auf ausreichend Freistellung zu achten.

Für das Wellenlöten wird in [2] die Gap-Ratio (Gleichung 1) zu 15-20% empfohlen. Für das Selektivwellenlöten ist aus den Versuchsreihen ein Wert von 35-40% zu empfehlen.

Hinsichtlich der Anbindung einer Kupferlage an die Durchmetallisierung, sollte darauf geachtet werden, massive Kupferlagen nur auf der Lotquellseite der Leiterplatte anzubringen. Anbindungen im inneren oder auf der Lotzielseite müssen insbesondere bei größeren Lagendicken (je nach Situation ab 70 µm) und bei Bauteilen mit großer thermischer Kapazität mit Wärmefallen und/oder thermischen Vias versehen werden.

#### Siwolak-Tool

Zur Berechnung des Gesamtprozesses in einem Modell muss das Bauteil und der Lagenaufbau zusammen mit den Prozessbedingungen abgebildet werden. Dafür müssen die thermischen Eigenschaften von Bauteilpin sowie dem Lagenaufbau in der Lötstelle modelliert werden. Zu diesem Zweck werden thermische Ersatzschaltbilder definiert. Durch die geeignete Parametrisierung dieser Ersatzschaltbilder können verschiedene Bauteile und Lötstellen sowie deren Verhalten im Lötprozess abgebildet werden.

Für das Bauteil wird ein von Klein-Wassink in [3] vorgeschlagenes Modell eingesetzt. Dabei werden die thermische Kapazität des Pins sowie der thermische Widerstand im Bauteilkörper vernachlässigt. Zur Modellierung verschiedener Lagenaufbauten werden die Kupferschichten und deren Anbindung an die Durchmetallisierung lagenweise nach thermischem Widerstand und thermische Kapazität charakterisiert. Der Mehrlagenaufbau wird dann wieder zu einem Gesamtaufbau zusammengesetzt,

sodass die jeweils untere Lage die darüber liegende heizt. Damit kann die sukzessive Aufheizung des Lagenaufbaus abgeschätzt werden. Unter der Annahme, dass das Lot im Lotspalt bis zu dem Punkt steigt, an dem die Lotschmelztemperatur unterschritten wird, kann ein zeitlicher Verlauf des Lotdurchstiegs in Abhängigkeit des Lagenaufbaus beurteilt werden, wie in

Bild 4 beispielhaft illustriert.

Die Validierung des Modells anhand von Lötversuchsdaten zeigt eine mittlere Abweichung von 20-30% zwischen Lötversuch und analytischer Vorhersage. Vor dem Hintergrund, dass die Standardabweichung im Prozess im Bereich von 5-15% liegt und die Beurteilung des Lotdurchstieges auf manueller optischer oder röntgentechnischer Begutachtung basiert, ist das Tool trotz der Abweichung eine Hilfestellung zur quantitativen Beurteilung und Identifizierung thermisch kritischer Lötstellen.

Bild 4: Bedienfeld des Siwolak-Tools mit Definition des Lagenaufbaus mit bis zu 6 Lagen, Auswahl des Bauteils, Definition der Lötparameter und Ergebnisplot des Lotdurchstiegs

#### **Zusammenfassung und Ausblick**

Der Selektivwellenlötprozess ist ein weit verbreiteter Lötprozess in mischbestückten Flachbaugruppen. Der Lötprozess ist hinsichtlich des Gesamtprozesses der Flachbaugruppenfertigung als kritisch zu betrachten, da die Lötqualität erheblich vom Lötstellendesign beeinflusst wird. Die erzielten Ergebnisse verdeutlichen das Potenzial des Einsatzes von Modellen in der Leiterplattenentwicklung zur Reduktion von Designschleifen, Fertigungsproblemen und Ausschuss.

Weitere vielversprechende Projekte zur automatisierten Bewertung von zusammenhängenden Leiterplattendesigns im Gesamtzusammenhang mit Hilfe von maschinellen Lernverfahren befinden sich in der Antragsphase.

Für Fragen steht der Autor gern unter der angegebenen E-Mail bereit.

### Literaturverzeichnis

- [1] SEIDEL, R. und J. FRANKE. THT-Problemstellen frühzeitig erkennen Simulative und experimentelle Untersuchung des Selektivwellenlötprozesses. In: *Schweißen und Schneiden*. Düsseldorf: DVS Media GmbH, 2021, S. 772-777

- [2] CHANG, S., R. WANG, Y. XIANG, P. WANG und W. SHI. Design for manufacturability of PTH solder fill in thick board with OSP finish. In: 2011 12th International Conference on Electronic Packaging Technology and High Density Packaging: IEEE, 8. August 2011 11. August 2011, S. 1-8. ISBN 978-1-4577-1770-3

[3] KLEIN WASSINK, R.J. *Soldering in Electronics*. 2. Aufl. Saulgau/Württ.: Leuze, 1991. ISBN 3-87480-066-0